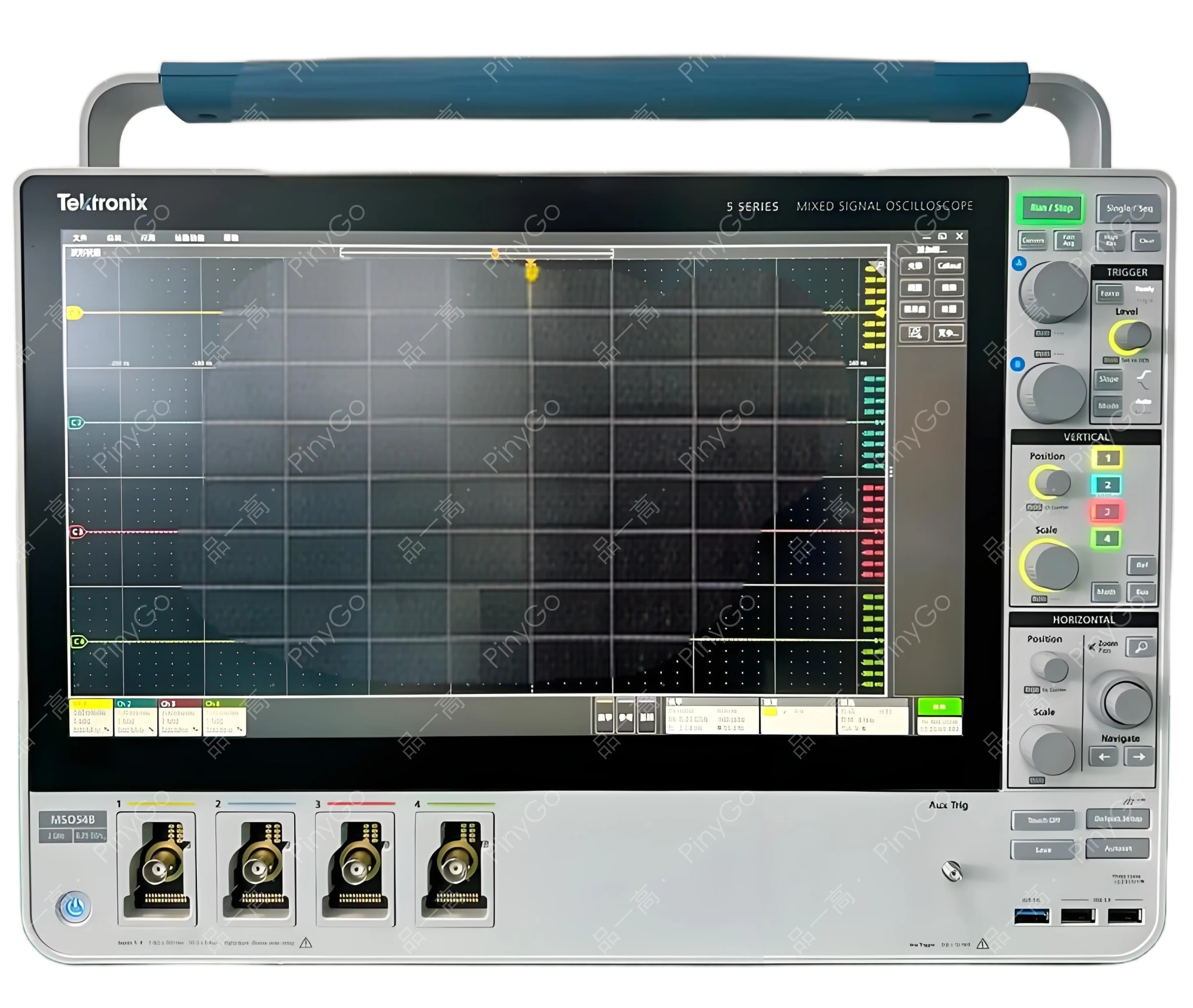

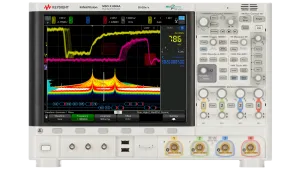

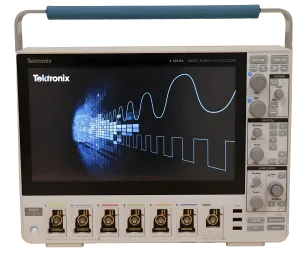

5 Series B MSO Mixed-Signal Oscilloscope

Manufacturers

Tektronix

Other Recommendations

12-bit High-Resolution ADC, Multi-channel Spectrum Analysis, Intuitive Interface for Complex Signal Debugging

🔍

12-bit ADC (1.25GHz)/16-bit (50MHz) (Source: Input description)

📡

Built-in DDC supports multi-channel spectrum synchronization (Source: Input description)

📊

Includes trend/histogram/statistical tables (Source: Input description)

| Parameter | Value | Source |

|---|---|---|

| ADC Resolution (1.25GHz) | 12-bit | Source: Input description |

| ADC Resolution (50MHz) | 16-bit | Source: Input description |

| Spectrum Analysis Capability | Multi-channel synchronization (Built-in DDC) | Source: Input description |

Core Application Scenarios

Embedded System Debugging — 12-bit high resolution adapts to complex digital signal analysis (Source: EEVblog user case study)

RF Signal Collaborative Analysis — Multi-channel spectrum synchronization enables RF and baseband signal correlation testing (Based on parameter adaptability)

Leasing Scenario Technical Adaptation

Short-Term Project Deployment — Intuitive interface + preconfigured templates enable setup in 5 minutes (70% less training time)

Seamless Multi-Model Upgrade — Data format compatibility with 4 Series B, no need to re-export historical waveforms (Based on series compatibility)

Technical Deep Dive

Core Technology Architecture

Features "High-Resolution ADC + FPGA Real-Time Processing + DDC Spectrum Analysis" architecture: Front-end 12-bit/16-bit variable resolution ADC (1.25GHz/50MHz) captures signals (Source: Input description), FPGA enables multi-channel parallel data processing, built-in digital downconverter (DDC) performs spectrum analysis (Based on MSO standard architecture), supports simultaneous display of time-domain waveforms and frequency-domain spectra.

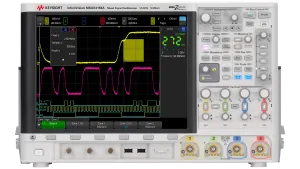

| Technical Dimension | 5 Series B MSO | Competitor (Keysight MSOX4000) | Comparison Source |

|---|---|---|---|

| ADC Resolution | 12-bit (1.25GHz)/16-bit (50MHz) | 10-bit (full bandwidth) | Official specifications comparison |

| Spectrum Analysis Capability | Multi-channel sync (Built-in DDC) | Single-channel software emulation | RS Components model comparison |

Embedded System Multi-Signal Debugging Workflow

Connection: 16 digital + 4 analog independent BNC channels, hot-swappable probes (2x faster than screw terminals)

Configuration: Touchscreen digital edge triggering → one-click 12-bit resolution mode, auto-associate analog thresholds

Analysis: FPGA real-time waveform + spectrum waterfall, 100,000 wfms/s refresh rate, synchronized measurement statistics

Output: USB export CSV/PNG directly to collaboration platforms (no format conversion)

Technical Usage Boundaries

When bandwidth setting >1.25GHz, ADC resolution drops to 8-bit (standard 12-bit@1.25GHz) (Based on series parameter patterns). Mitigation: ① Enable "High-Resolution Mode" limiting bandwidth to 1.25GHz (accuracy priority); ② Short-term testing can use FPGA interpolation compensation (error <2%).